Sata Spread Spectrum

⚡ 👉🏻👉🏻👉🏻 INFORMATION AVAILABLE CLICK HERE 👈🏻👈🏻👈🏻

App Note: Spread Spectrum Clocking and Serial ATA

May 11, 2005

Summary

Serial ATA (SATA) attached HDDs are targeted at the low-cost desktop market.

Additional Formats

PDF

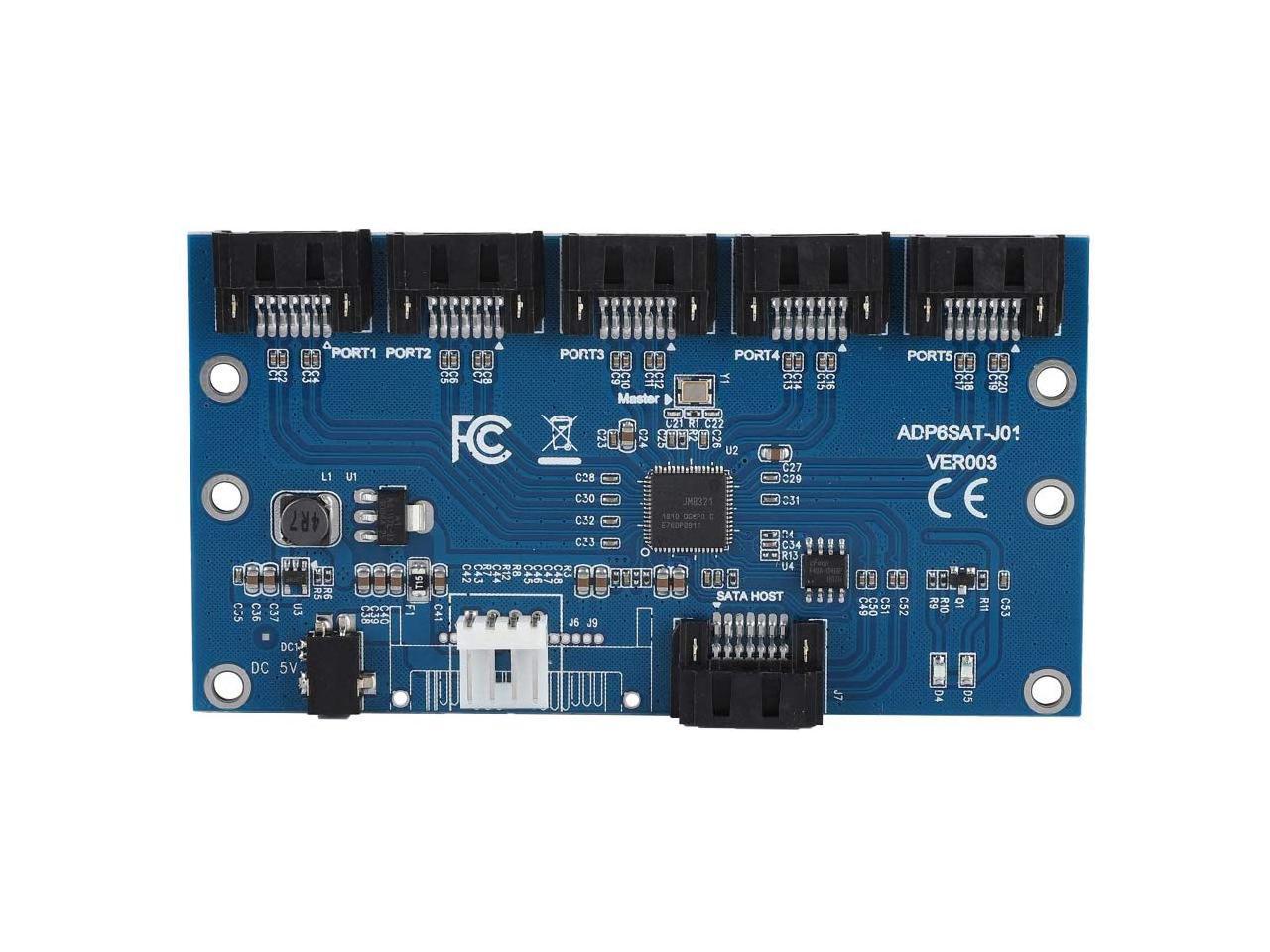

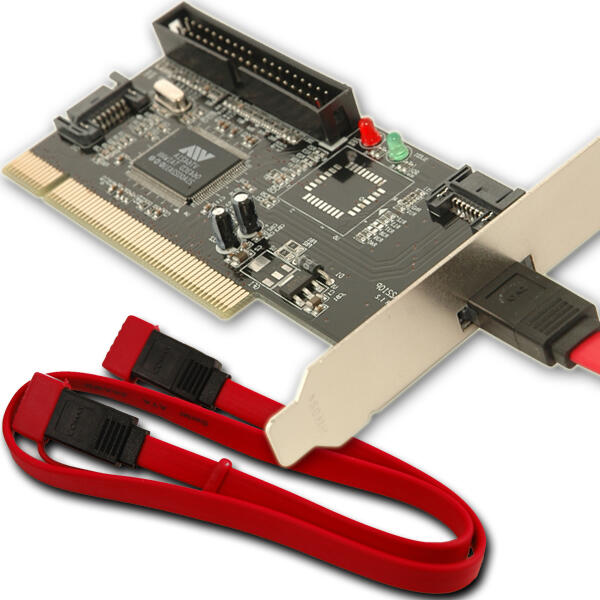

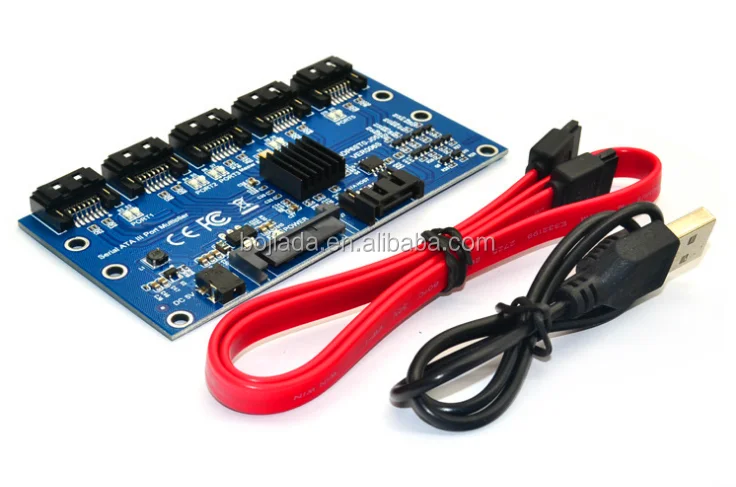

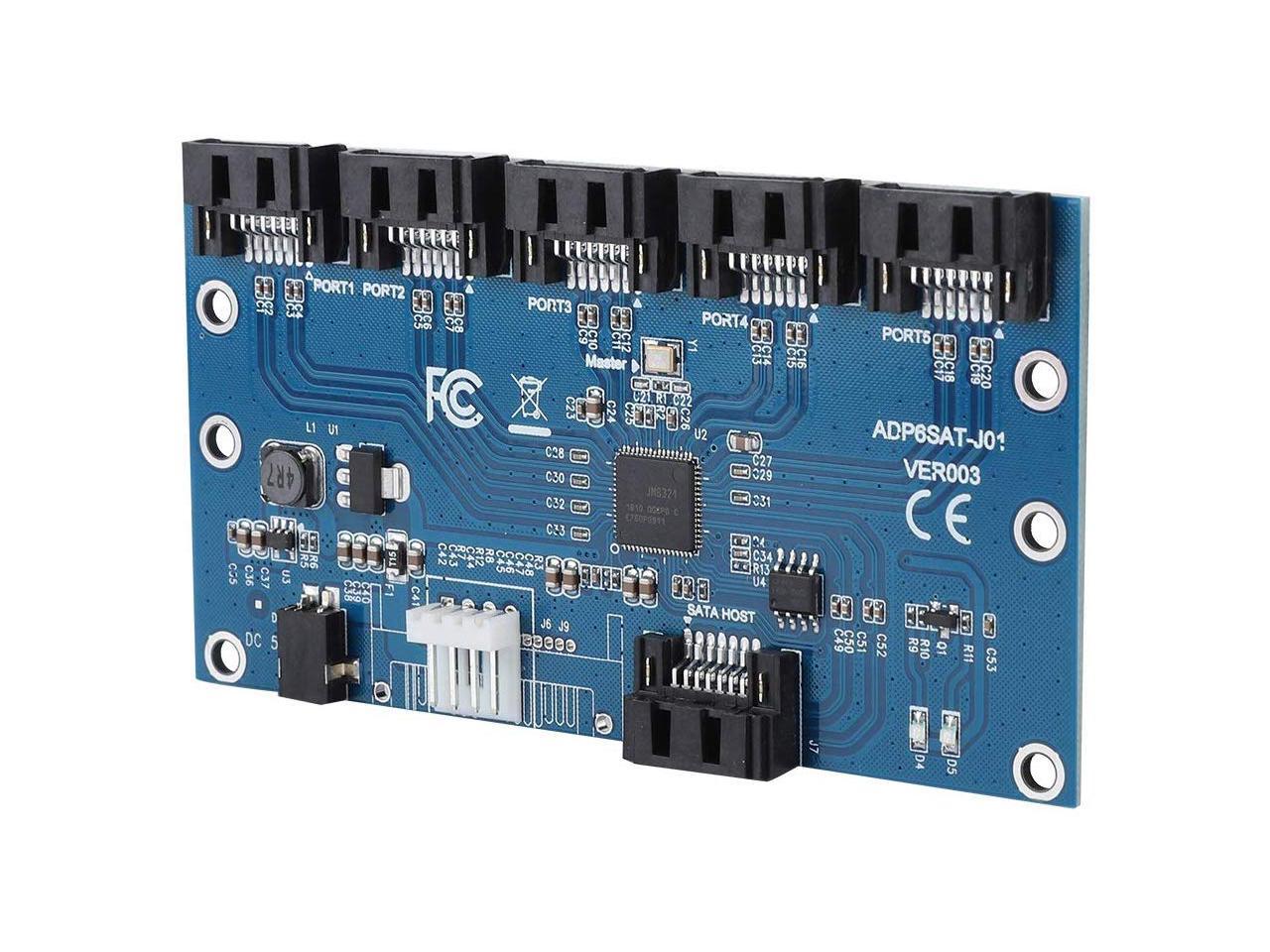

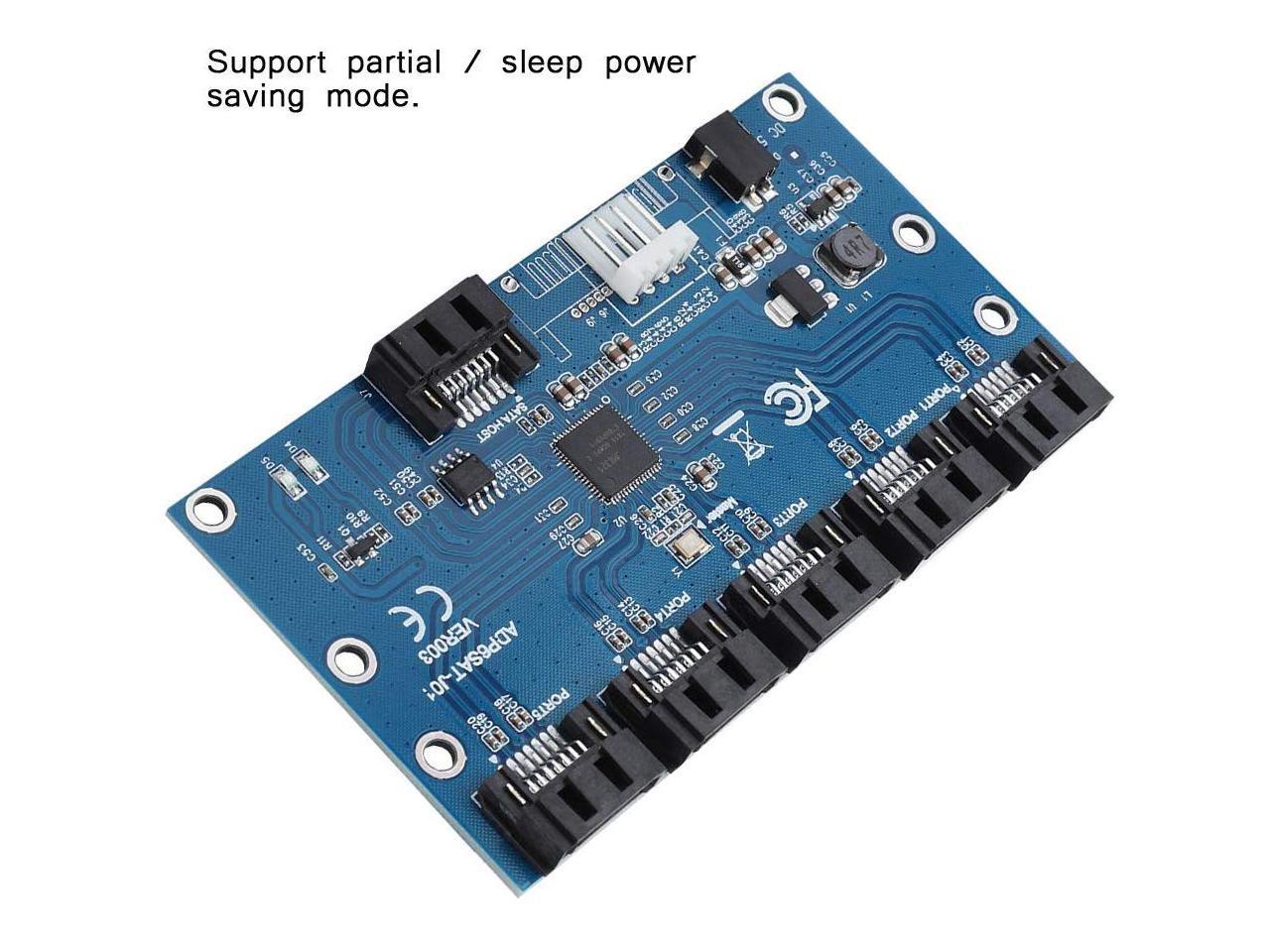

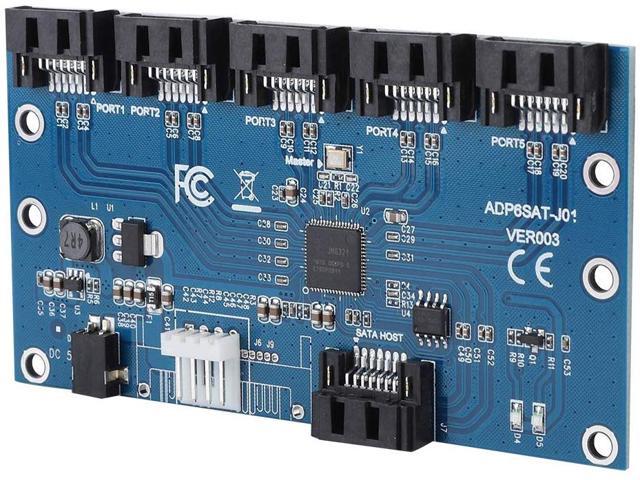

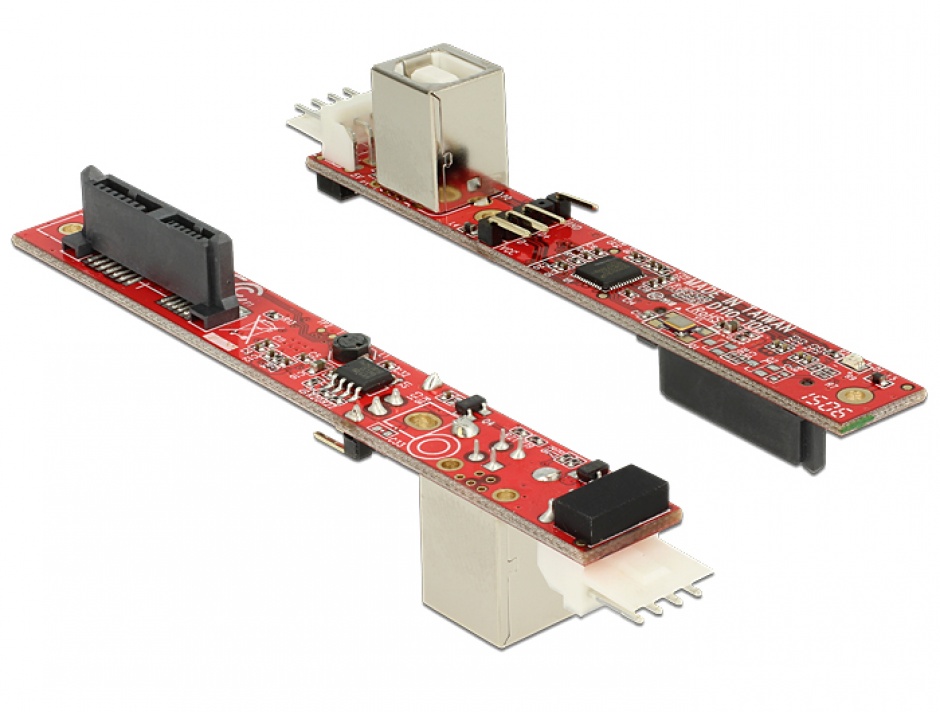

Serial ATA (SATA) attached HDDs are targeted at the low-cost desktop market. One of the components in the SATA connected system is the SATA internal cable itself. These cables are thin, easy to connect and disconnect and provide improved cooling efficiency with less airflow obstruction. To keep costs down, these internal cables are not designed with shielding for EMI. However at the desktop enclosure level, the radiated energy should be kept below specified limits to avoid interfering with radio equipment. Spread Spectrum Clocking (SSC) technique helps keep the EMI levels low on Serial ATA cables.

If a very tightly controlled clocking scheme is used, the radiated energy tends to concentrate in very few frequency values. The radiated emission could exceed limits at these few frequencies. However, by intentionally making the clock drift within a specified range, the average energy emitted at any given frequency is reduced profoundly. The sample diagram shows this effect. The drift introduced on the edges is well within the range of Phase Locked Loops used to provide proper clocking to recover parallel data from the serial stream.

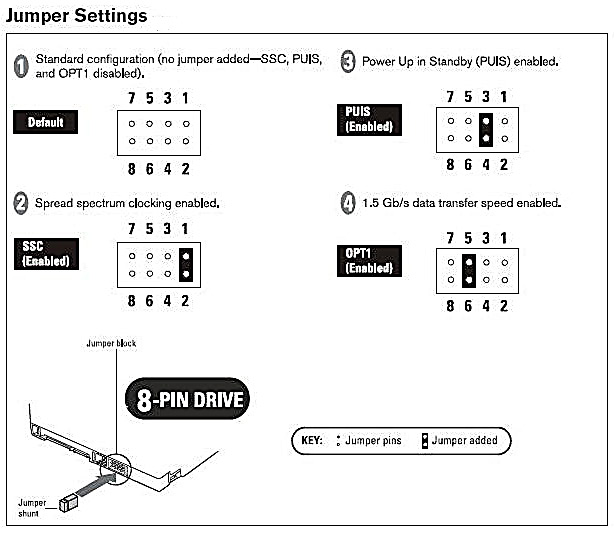

SSC is accomplished by “down-spreading” the clock frequency using a deviation of no more than 0.5% down-spread (+0% -0.5%) Δ = peak reduction

The CATC SATracer v1.4 analyzer, and later versions, can record traffic from Serial ATA devices that utilize spread spectrum clocked (SSC) signaling. SSC modulates the operating frequency of a circuit slightly to spread its radiated emissions over a range of frequencies rather than just one tone. By distributing emissions for a given frequency, SSC transmissions help devices meet FCC requirements.

The Serial ATA I Specification states that SSC transmission is optional on the transmitter (TX) side for both host and device. However, SSC is a mandatory capability for all Serial ATA receivers (RX). This requirement eliminates compatibility issues by ensuring that all Serial ATA devices can tolerate SSC signals when attached to a device that transmits SSC signaling.

CATC’s SATrainer traffic generator for Serial ATA, released in July of 2003, allows spread spectrum transmissions to be enabled/disabled dynamically while generating traffic. This is a valuable capability for validating SSC operation for both host and device side silicon.

Sources:

Serial ATA Specification 1.0 Copyright 2001 (All Rights Reserved)

Serial ATA Working Group

Conference: Custom Integrated Circuits Conference, 2007. CICC '07. IEEE

This person is not on ResearchGate, or hasn't claimed this research yet.

This person is not on ResearchGate, or hasn't claimed this research yet.

To read the full-text of this research, you can request a copy directly from the authors.

To read the full-text of this research, you can request a copy directly from the authors.

A new spread spectrum clock generator (SSCG) using double modulation is presented in this paper. Not only the divider is varied, but also the voltage controlled oscillator is modulated. This technique can enhance the modulation bandwidth so that the effect of EMI suppression is improved and can optimize the jitter caused by the SigmaDelta modulator. In addition, the method of two-path is applied to reduce the capacitance value such that the total integration can be achieved. The proposed SSCG has been fabricated in a 0.18 mum CMOS process. The clock of 1.5 GHz with down spread ratio of 0.5% is realized for applications to serial ATA. The 19.63dB EMI reduction (RBW=10 KHz) and 35 ps-pp period jitter are achieved in this study. The size of chip area is 0.44times0.48 mm2. The power consumption is 27 mW.

To read the full-text of this research,

you can request a copy directly from the authors.

... The serialto-parallel converter (S/P) converts from the DATA to the received parallel data (RD) by using the CLK. In this SATA-PHY, the SSCG is applied a fractional SSCG because of a large EMI reduction [2][3][4][5][6][7][8][9][10][11][12][13][14][15][16][17][18]. The fractional SSCG should be narrow loop bandwidth because the quantized noise originated from a ΣΔ modulator is removed. ...

... The VCO frequency is thus modulated by the triangular wave. This SSCG can reduce EMI more substantially than other SSCGs because the linearity of the modulation can be obtained accurately by utilizing the logic circuits [2][3][4][5][6][7]. This SSCG has two main jitter sources. ...

... However, their output jitter is still large because their digitally controlled ring oscillators generate large jitter and it is difficult to operate them accurately if there are PVT variations. The capacitance multiplication technique has been presented to reduce the design area as an approach in which the operation is based on that of a conventional SSCG [2,7,20]. However, the settling time is necessarily long because the loop bandwidth is set to be narrow. ...

A low-jitter fractional spread-spectrum clock generator (SSCG) utilizing a fast-settling dual-charge-pump (CP) technique is developed for serial-advanced technology attachment (SATA) applications. The dual-CP architecture reduces a design area to 60% by shrinking an effective capacitance of a loop filter. Moreover, the settling-time is reduced by 4 μs to charge a current to the capacitor by only main-CP in initial period in settling-time. The SSCG is fabricated in a 0.13 μm CMOS and achieves settling time of 3.91 μs faster than 8.11 μs of a conventional SSCG. The random jitter and total jitter at 250 cycles at 1.5 GHz are less than 3.2 and 10.7 psrms, respectively. The triangular modulation signal frequency is 31.5 kHz and the modulation deviation is from −5000 ppm to 0 ppm at 1.5 GHz. The EMI reduction is 10.0 dB. The design area and power consumption are 300 × 700 μm and 18 mW, respectively.

... Poor results are given by a simple sinusoidal ξ(t) signal; better performances can be achieved with a triangular waveform; while we can get even better performances with a more complicated periodic driving signal [3]. Recently, many papers in literature proposed a 1.5 GHz spread spectrum clock generator for SATA-II [4], [5], [6], [7] employing a triangular waveform as modulating signal. Almost all of them are based on a fractional PLL employing a ∆Σ modulator. ...

... In the same table we also compared results from our prototype with results from other solutions in literature. All prototypes in [4], [5], [6] exploit a triangular modulation. Our prototype achieves the best performances in terms of power consumption and EMI reduction. ...

This paper proposes a prototype of a spread spectrum clock generator which is the first known specifically meant for 3 GHz Serial ATA-II applications. The modulation is obtained from a fractional PLL which employs a Delta-Sigma modulator. A further innovative aspect of our work is that our prototype takes advantage of a chaotic PAM as driving signal, instead a triangular signal as in all spread spectrum generators proposed in literature for SATA-II. In this way we avoid the periodicity of the modulated clock, completely flattening the peaks in the power spectral density. The circuit prototype has been designed in 0.13 mum CMOS technology and achieves a peak reduction greater than 14 dB measured at RBW = 100 kHz. The chip active area is 0.27times0.78 mm2 and the power consumption is as low as 14.7 mW.

A microstrip line fed star-star fractal antenna with notch loaded semi-elliptical ground plane is presented for super wideband applications. An impedance bandwidth of 4.6–52 GHz, i.e., a bandwidth ratio of 11.31:1 is achieved for VSWR < 2. The antenna structure has advantages of compact dimensions and wider bandwidth over previously reported SWB structures. Radiation characteristics, i.e., co and cross polar radiation patterns, peak gain, and efficiency has been presented and discussed. The simulated and experimental results are found to be good agreement. © 2017 Wiley Periodicals, Inc. Microwave Opt Technol Lett 59:624–630, 2017

In this paper, a 6-GHz frequency synthesize (FS) for SATA III application by using 0.18-μm CMOS technology is presented. Multi-modulus divider (MMD) is utilized to achieve the function of spreading spectrum of SATA III. The complementary voltage-controlled oscillator (VCO) is adopted for phase noise consideration. In order to reduce the locking time of spreading spectrum, the loop bandwidth is increased as large as possible. Based on the aforementioned techniques, the measured free-running phase noise and closed-loop phase noise of the proposed FS are −112 dBc/Hz and −80 dBc/Hz at 1-MHz offset frequency, respectively. The total dc power consumption is 25.2 mW.

A technique that enables a SSCG to fine-tune an output signal frequency and a spread ratio is presented. Proposed SSCG achieves the output signal frequency from 1.2 GHz to 3.0 GHz and the spread ratio from 0 to 30000 ppm. The fine-tuning technique achieves 30 ppm adjustment of the output signal frequency and 200 ppm adjustment of the spread ratio. This technique is achieved by controlling a triangular modulation signal characteristics generated by a proposed digital controlled wave generator. A proposed multi-modulus divider can have a divide ratio of 4/5 and 8/9. This SSCG has been fabricated in a 0.13-μm CMOS process. The output signal frequency-range and the spread ratio are achieved fluently from 0.1 to 3.0 GHz and from 0 to 30000 ppm, respectively. EMI noise is suppressed at less than 17.1 dB at the output signal frequency of 3.0 GHz and spread ratio of 30000 ppm. Copyright © 2013 The Institute of Electronics, Information and Communication Engineers.

A 6-GHz phase-locked loop based spread-spectrum clock generator employing a self-oscillating technique is proposed. The clock generator adopts the property of the inherent oscillation of a charge-pump PLL while introducing no extra quantization noise. With the amplitude and frequency control, modulation frequency and frequency deviation can be tuned at 31.5 kHz and 5000 ppm, respectively. The measured EMI reduction is 12.5 dB at the 100-kHz resolution bandwidth. The measured root mean square jitter is 2 ps and peak-to-peak is 15 ps. This work was fabricated in a 90-nm digital CMOS technology, occupies 0.54 ${rm mm}^{2}$ and consumes 14.4 mW from a 1.2-V supply.

In this paper, a small area spread-spectrum clock generator (SSCG) with high EMI reduction for SATA-3.0 is presented. Conventional methods use inductor-capacitance (LC) tank to fulfill the high frequency requirement for SATA-3.0. However, the monolithic inductors always occupy a large area, and required precisely characteristic for different fabrication processes. This research propose a SSCG using a ring voltage-controlled oscillators (Ring-VCO) at 6GHz operating frequency; By using the proposed Ring-VCO, the active area of SSCG is 65% of comparable LC tank implementations, and Ring-VCO is much easier to characterized for any CMOS process. In addition, a multi-stage-noise-shaping (MASH) delta-sigma modulator (ΔΣ modulator) is used to reduce fractional spurs and quantization error for high EMI reduction. The chip is designed in TSMC 0.18um 1P6M CMOS process with active area of 500um×300um, and the simulation results consumes 60.43mW with 1.8V supply. The peak-to-peak jitter at 6GHz output of non spread-spectrum is 6.16ps, and the EMI reduction is 22.49dB with 5000ppm down spread to 5.97GHz.

A low-jitter fractional spread-spectrum clock generator (SSCG) by utilizing a fast-settling dual charge-pump (CP) technique has been developed for Serial-ATA (SATA) applications. The proposed fast-settling dual CP technique not only reduced a design area but also shortened settling-time by controlling the CP operation sequence in an SSCG settling period. A multi-modulus divider using differential dynamic flip-flops was applied to our SSCG to reduce the design area, power consumption, and jitter. The proposed SSCG for SATA generation I was fabricated in a 0.13 mum CMOS process. The settling-time was 3.91 mus faster than that of a conventional SSCG, 8.11 mus. The random jitter and total jitter in 250 cycles at 1.5 GHz were 2.7 psrms and 3.3 psrms, respectively. The EMI reduction that meets SATA specification was 10.0 dB. The design area and the power consumption were 300 times 700 mum2 and 18 mW, respectively.

A new technique utilizing two-point (TP) modulation for a spread spectrum clock generator (SSCG) for serial advanced technology attachment is presented in which the divider ratio is varied by a digital SigmaDelta modulator, and the voltage-controlled oscillator is modulated analogically. With this technique, the modulation bandwidth is enhanced in order that the modulation profile accuracy and jitter performance caused by the SigmaDelta modulator can be improved at the same time. The order of the SigmaDelta modulator and the loop filter can be reduced to save power and area, while the electromagnetic interference (EMI) suppression still satisfies specifications. The dual-path loop filter (DL) reduces the size of the loop capacitor and enables full integration. The proposed TPDL-SSCG has been fabricated in a 0.18 mum CMOS process. The size of the chip area is 0.44 times 0.48 mm2. The circuit produces a clock of 1.5 GHz with a down-modulation ratio of 0.5%, 10.14 dB EMI of reduction, 5.485 ps rms jitter, and 35 ps peak-to-peak jitter. The power consumption, excluding an output buffer, is only 15.3 mW.

A new spread spectrum clock generator (SSCG) using two-point delta-sigma modulation is presented in this paper. Not only the divider is varied, but also the voltage controlled oscillator is modulated. This technique can enhance the modulation bandwidth so that the effect of EMI suppression is improved. In addition, the method of two-path is applied to the loop filter to reduce the capacitance value such that the total integration can be achieved. The proposed SSG has been fabricated in a 0.35mum CMOS process. The clock of 400MHz with center spread ratios of 1.25% and 2.5% are verified. The size of chip area is 0.90times0.89mm2.

A multi-rate transceiver incorporating TX slew control with >2times range, PLL with <0.5times loop-filter area using capacitance multiplication, and DeltaSigmaZ-SSCG having 11.7dB peak reduction is designed in 0.13mum CMOS. Occupying 2.33mm2 with TX operable up to 8.5Gb/s, the quad transceiver consumes 386mW from 1.2V supply and has a BER<10-14 at 6Gb/s over an 8m cable with 22dB loss

In this paper, we proposed a spread spectrum clock generator (SSCG) for the Serial AT Attachment Generation 2 (SATA-II). We use a fractional-N PLL to accomplish the spread spectrum function. The SSCG integrates a conventional PLL, a digital 3rd order MASH 1-1-1 delta-sigma modulator and an address generator. The SSCG generates clocks at 1.5 GHz, a 5000 ppm down spread with a triangular waveform frequency modulation of 33 kHz. The circuit has been simulated in 0.18 μm CMOS technology. The non spread spectrum clocking has a jitter of 80 ps and the peak amplitude reduction is 23.44 dBm in spread spectrum mode. The power dissipation from a 1.8 V supply is 55 mW.

A spread-spectrum clock generator (SSCG) using fractional-N phase-locked loop (PLL) with an extended range sigma-delta (Sigma Delta) modulator is presented in this paper. The proposed Sigma Delta modulator simply adds an extra output bit in the first stage modulator. It can enlarge the input range about three times as compared to the conventional modulator and solve the saturation problem when the input exceeds the boundary of the conventional modulator. A flexible digital modulation controller can generate center and down spread-spectrum modulation and each has spread ratios of 0.4%, 0.8%, 1.6% and 3.2%. The proposed SSCG has been fabricated in TSMC 0.35-mu m double-poly quadruple-metal CMOS process with output frequency of 300 MHz. The active area is 0.63 x 0.62 mm(2) and the power consumption is 17.5 mW.

We have developed a spread-spectrum Phase-Locked Loop (PLL) for serial Advanced Technology Attachment (ATA) applications. We investigated the relation between the output jitter of PLLs in serial ATA applications and Σ Δ modulators in PLLs. On the basis of this study, we developed a spread-spectrum PLL for serial ATA applications and achieved a combination of small jitter and large electromagnetic interference (EMI) peak power reduction. This was achieved using two key components: multi-bit Σ Δ-controlled PLL and voltage-controlled oscillation with cross-coupled load delay cells. Using a 0.15-μm complementary metal-oxide semiconductor process, we fabricated a complete serial ATA transceiver featuring a spread-spectrum clock generator (SSCG). We achieved a spread-spectrum PLL with 10-dB EMI reduction and 8.1 ps random jitter for use in serial ATA applications. All other measured results for SSCG performance were very good and showed that the spread-spectrum generator more than satisfies serial ATA specifications.

A low-jitter 5000ppm spread-spectrum clock generator is implemented in a 0.18μm CMOS process. By using 10 multi-phase clocks and a ΔΣ modulator with periodic input, the chip has a deterministic jitter of 25ps due to spread-spectrum clocking and an amount of spreading of 5000ppm.

This paper describes a spread spectrum clock generation (SSCG) PLL that uses a dual-tone modulation profile. The proposed modulation profile consists of the weighted sum of triangular waves. A mathematical analysis is applied to find out the optimum weight. Experimental results show that the Δ-Σ fractional-N PLL with the clock modulator exhibits better performance than a traditional SSCG by more than 2dB at the 630MHz operation.

We have developed a 5000 ppm spread spectrum Serializer/Deserializer (SerDes) physical layer (PHY) chip compliant with Serial AT Attachment (ATA). The chip was fabricated with a 0.15 μm 1.5 V CMOS process and includes a self-running spread spectrum carrier generator to provide both transmit and receive block, a self-running phase interpolator to recover the +/-5000 ppm spread spectrum receive (RX) clock and data.

We have successfully developed a 5150 ppm spread spectrum Serializer / Deserializer (SerDes) physical layer (PHY) chip compliant with the Serial AT attachment (ATA). The device was fabricated with a 0.13 mum, 1.5V CMOS process and includes a self-running, pulse-swallow phase-locked loop (PLL) to generate the transmit (TX) carrier, a triple loop tracking the PLL to recover the receive (RX) clock, and a 0.3 mW current-crossover level detector to detect the 1.5 Gbps carrier for initial communication.

In this paper, we present an explicit model for the MOS capacitor in accumulation and comp

Cum Sperm Pussy The Pornmad

German Russian Dictionary

Jules Jordan S

Xhamster Milf Blonde

Massage Japanese Student Sex

App Note: Spread Spectrum Clocking and Serial ATA

Tech ARP - SATA Spread Spectrum

A New Spread Spectrum Clock Generator for SATA Using ...

hard drive - Should I use "Spread Spectrum Clocking" on my ...

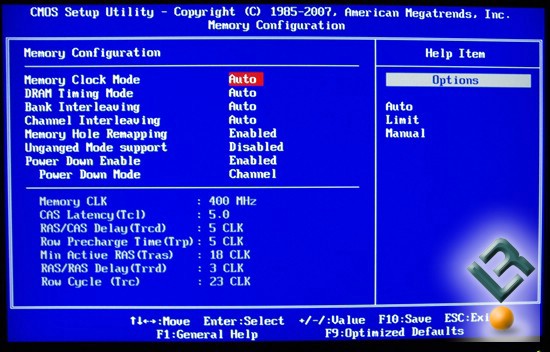

Complete BIOS Tuning Guide - "Spread Spectrum Control ...

Sata Spread Spectrum | ★MERCEDES GL&GLK-The Be…

Методы расширения спектра — Википедия

CPU Spread Spectrum - biosgid.ru

Sata Spread Spectrum