Хакер - AEPIC Leak. Изучаем нашумевшую уязвимость в процессорах Intel

hacker_frei

Валентин Холмогоров Юрий Язев

Содержание статьи

- Что такое Intel SGX?

- Брешь Aepic Leak

- Выявление уязвимости

- Цели атаки

- Немного теории

- Архитектура Intel SGX

- Эксплуатация

- Насколько это опасно?

- Как обезопасить свои данные?

Программно эксплуатируемая аппаратная уязвимость — явление редкое. Обнаружить такую непросто, а пофиксить — еще сложнее: если проблема скрывается в архитектуре процессора, она вполне может оказаться и вовсе неустранимой. Технология Intel SGX уже неоднократно подвергалась атакам, и вот недавно объединенная группа исследователей обнаружила в процессорах Intel еще один архитектурный баг, позволяющий организовать утечку ключей шифрования и другой критичной информации.

Баг получил наименование AEPIC Leak. Давай разберемся в его устройстве и посмотрим, так ли он опасен, как об этом говорят.

ЧТО ТАКОЕ INTEL SGX?

Технологию SGX (Software Guard Extensions) называют краеугольным камнем системы безопасности процессоров Intel. По большому счету SGX представляет собой набор инструкций, позволяющих программам, в частности операционным системам и виртуальным машинам, создавать так называемые анклавы — защищенные участки памяти для хранения ключей шифрования и прочих критичных данных.

Главная особенность анклавов заключается в том, что, кроме процесса‑владельца, ни один другой процесс, включая ядро ОС, гипервизоры виртуальных машин, периферийные устройства, обращающиеся к памяти с прямыми запросами DMA, не имеют прав на чтение из защищенной области памяти и запись в нее. Это гарантирует целостность хранящихся там данных.

Теоретически нет никакой возможности изменить содержимое анклавов SGX, даже если сама операционная система скомпрометирована или в ней работает вредоносное ПО с высокими привилегиями. С использованием этого инструмента можно организовать надежное шифрование данных (например, для создания защищенных дисковых разделов), выполнять безопасные удаленные вычисления, хранить цифровые сертификаты или реализовать системы защиты от копирования — так, SGX активно использовался в технологии записи данных Blu-ray. Изначально SGX создавался именно для вычислений на удаленных машинах в обособленном и полностью защищенном окружении.

SGX появилась в 2015 году в процессорах Intel шестого поколения Skylake. Именно в эти чипы был встроен аппаратный модуль Memory Encryption Engine, обеспечивающий шифрование данных, которые передаются от процессора в анклавы памяти SGX. Поскольку шифрование выполнялось компонентом CPU, периметр безопасности ограничивался только процессором, без обмена незашифрованными данными с оперативной памятью, всегда считавшейся ненадежной в плане информационной безопасности.

БРЕШЬ AEPIC LEAK

AEPIC Leak — первый архитектурный баг CPU, позволяющий атакующему сливать данные из процессора без использования стороннего канала. Такие уязвимости, как Meltdown или Spectre, не являются полностью аппаратными багами. Они представляют собой аппаратные уязвимости, которые эксплуатируются из программного обеспечения. Следовательно, сторонний канал — это внешнее ПО. Другими словами, брешь AEPIC Leak позволяет уводить данные напрямую, без использования специальных программ. Тем не менее, чтобы создать эти данные, применяются специальные архитектурно зависимые библиотеки Intel IPP и SGX. Атаки на уязвимости Meltdown и Spectre называются атаками переходного исполнения из‑за необходимости использования такого специального софта.

К чисто архитектурным багам также относятся широко известные уязвимости FDIV и F00F. Первый из них был обнаружен в оригинальных процессорах Pentium и приводил к неверным результатам при делении чисел с плавающей запятой с помощью инструкции FDIV. Второй же присутствовал в большем числе моделей процессоров, включая всю линейку микроархитектурного ряда P5. Ошибка могла привести к останову процессора еще при загрузке операционной системы, а «лечили» это, обновляя ОС.

Между тем в девяностые годы прошлого века, когда были выявлены две эти уязвимости, диапазон вычислений не распространялся дальше локального компьютера. Поэтому, хотя выявление этих багов наделало много шума, умышленная их эксплуатация не создавала для пользователей серьезных проблем, особенно после выхода заплаток. В наше время картина выглядит иначе. Мир зависит от вычислений в облаках, а так как SGX — главный защитный механизм удаленных вычислений, эксплуатация хакерами его уязвимости наносит сокрушительный удар по конфиденциальности данных.

Выявление уязвимости

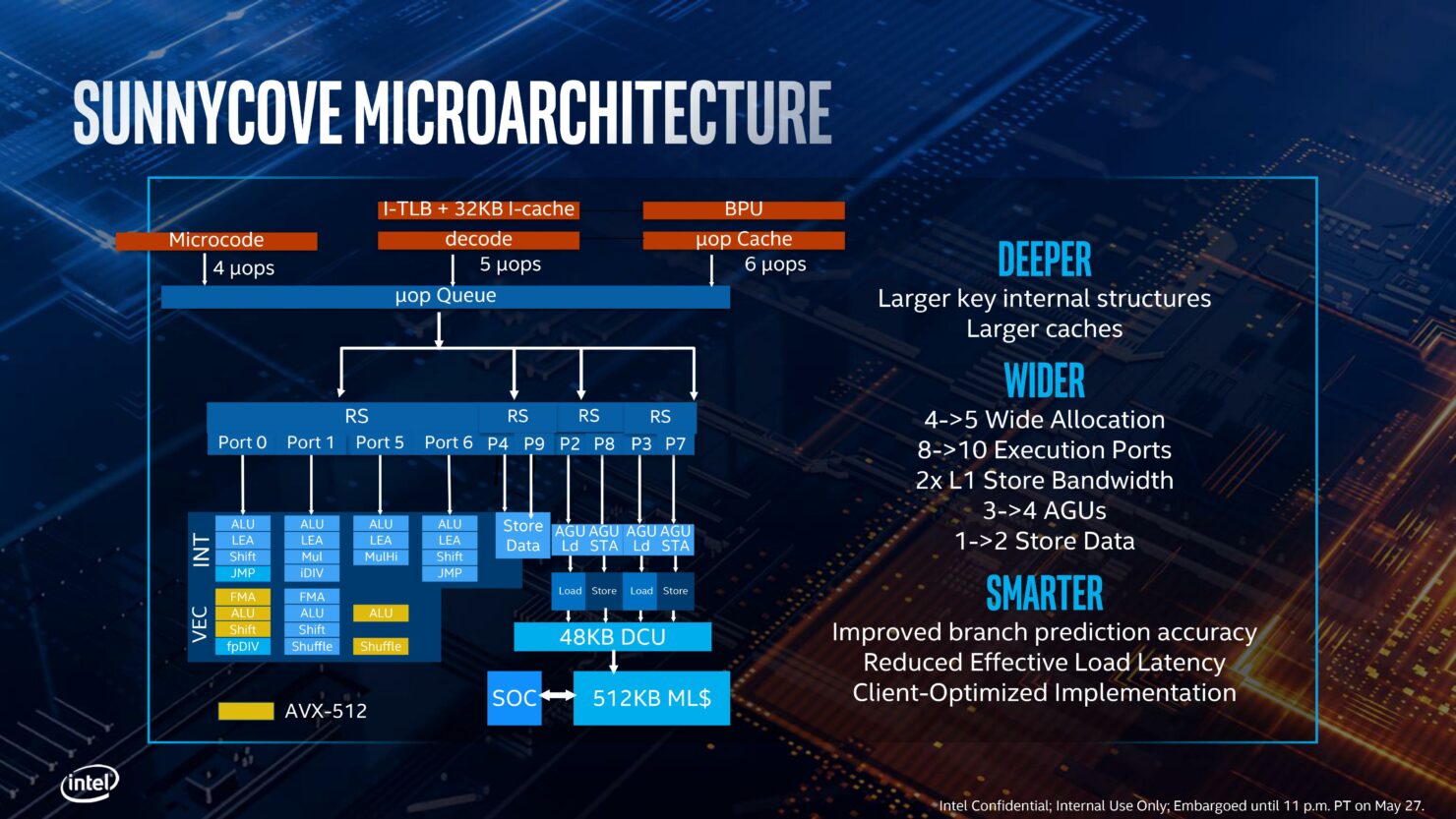

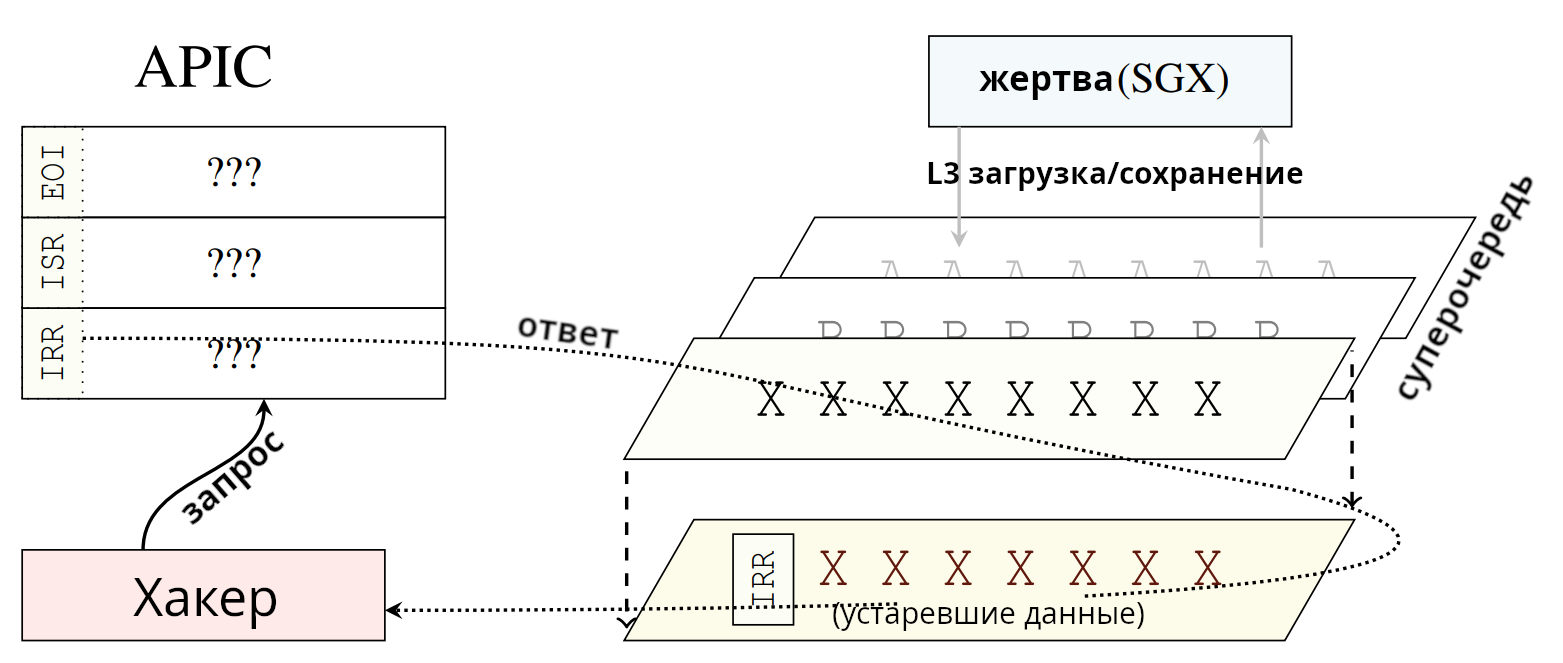

Исследователи просканировали адресное пространство ввода/вывода процессоров, базирующихся на микроархитектуре Intel Sunny Cove. В результате удалось обнаружить, что не все регистры локального APIC проинициализированы должным образом. Другими словами, после выполнения операции чтения/записи эти регистры не очищаются и продолжают хранить старые значения, которые использовались в предыдущем вычислении.

Посредством AEPIC Leak можно прочесть зарезервированную часть APIC-регистров. APIC использует суперочередь между L2 и LLC для передачи данных ядру процессора. Зарезервированная часть не перезаписывается, что позволяет хакеру прочесть устаревшие данные другого приложения.

Наиболее уязвимым участком передачи данных внутри CPU, откуда можно утянуть ценную информацию, является суперочередь — буфер для передачи данных из кеша L2 в LLC и обратно. При наличии административных привилегий в системе это позволяет похитить хранящиеся в анклаве SGX данные без использования сложных схем.

Цели атаки

Уязвимости AEPIC Leak подвержены все процессоры Intel на базе архитектуры Sunny Cove (такие как Ice Lake и Alder Lake), то есть клиентские микропроцессоры 10, 11 и 12-го поколений, а также серверные процессоры Xeon третьего поколения.

При этом сама Intel выкатила более широкий список процессоров, подверженных уязвимости AEPIC Leak, включающий Ice Lake Xeon-SP, Ice Lake D, Gemini Lake, Ice Lake U, Y и Rocket Lake.

Сведения о том, подвержены ли атакам на эту брешь процессоры фирмы AMD, разнятся. Кто‑то сообщает, что такие процессоры не имеют этой уязвимости, другие утверждают, будто атакам подвержены процессоры на архитектурах Zen 1–3.

Даниель Грусс (исследователь из группы Грацского технического университета, опубликовавшей отчет об уязвимости) утверждает, что, поскольку Apple M1 (и, возможно, M2) построены на основе того же дизайна, что и Sunny Cove, они тоже подвержены атакам на уязвимость AEPIC Leak.

Хотя установлено, что наибольшую опасность AEPIC Leak представляет для локальных систем, это не значит, что хакер не может на своем компьютере подготовить эксплуатирующую уязвимость малварь и подсунуть ее пользователю, работающему на целевой системе. Останется заставить пользователя запустить вредоносную программу, а дальше уже дело техники.

Как все‑таки работает уязвимость AEPIC Leak? Сейчас разберемся.

НЕМНОГО ТЕОРИИ

Современные процессоры — крайне сложные устройства, состоящие из набора логических элементов, управляемых собственным набором микропрограмм. Один из них — расширенный программируемый контроллер прерываний (APIC), управляющий, как следует из его названия, прерываниями. Он состоит из локального APIC, интегрированного в каждое логическое ядро и ответственного за обработку межпроцессорных прерываний, и внешнего APIC, управляющего прерываниями ввода/вывода.

В свою очередь, локальный APIC содержит так называемые регистры, предназначенные для управления его функциональностью или отображения состояния прерываний в системе. По умолчанию современные контроллеры APIC функционируют в режиме xAPIC, в котором каждый регистр представляет собой область размером 4 Кбайт в физическом адресном пространстве памяти. Разные модели процессоров имеют разное количество APIC-регистров: от 32 до 256.

Процессоры Intel используют иерархическую систему памяти для кеширования данных на нескольких уровнях. Кеш самого низкого уровня — наиболее близкого к ядру процессора (L1) — предоставляет более быструю память, чем кеши верхних уровней. Но этот кеш имеет небольшой объем и используется для хранения данных, которые готовятся для обработки процессором на следующем шаге. Также в нем хранятся данные, попутно выбранные из кеша верхних уровней.

Кеши более высоких уровней имеют больший объем, но отличаются меньшим быстродействием. В архитектуре Intel на самом низком уровне располагается кеш инструкций (L1I) и данных (L1D), на втором уровне — локальный объединенный кеш (L2). Кеш‑память последнего уровня (Last Level Cache, LLC или L3) обычно общая для всех физических ядер. В документации Intel последний уровень кеша именуется LLC, поскольку разные устройства имеют разное количество кешей. Так, если у вычислительных ядер центрального процессора по три уровня кеша, то видеоядро имеет четыре уровня.

Когда процессору нужны данные, он пытается их найти сначала на ближайшем уровне. Таким образом, в первую очередь он ищет их в собственных регистрах. Если там их нет, поиск продолжается на уровне L1. Если на этом уровне нужных данных тоже нет, процессор создает буфер, с помощью которого обращается на уровень L2, попутно записывая в этот буфер найденные данные или сведения о неудаче. Данные, изъятые из верхнего уровня, через буфер записываются на нижний и в итоге передаются процессору.

Если на уровне L2 тоже нет искомых данных, процессор создает суперочередь (superqueue) и через нее обращается на уровень L3, повторяя операции записи и логирования выполненных операций. Если же данных нет и на уровне L3, процессор обращается к контроллеру памяти, чтобы тот попытался найти их в оперативной памяти.

Этот круговорот данных между уровнями памяти получил название «кольцевое соединение». Как мы уже знаем, данные в анклаве передаются только по уровням процессорного кеша. Именно на него нацелены атаки, направленные на эксплуатацию уязвимости AEPIC Leak.

АРХИТЕКТУРА INTEL SGX

Технология Intel SGX в той или иной мере использует все эти архитектурные элементы. Intel Software Guard Extension обеспечивает доверенную среду исполнения (Trusted Execution Environment) на процессорах с архитектурой x86-64. Чтобы программное обеспечение могло доверять анклаву или анклав был уверен, что его пытается прочесть или записать процесс‑владелец, в архитектуре SGX предусмотрена процедура аттестации — криптографической проверки подлинности анклава. Различают локальную и удаленную аттестацию: первая применяется для проверки анклавов на одной платформе, вторая — при удаленных вычислениях.

Во время создания анклава CPU собирает криптографические измерения для запуска анклава и его сигнатуры в два измерительных регистра: MRSIGNER и MRENCLAVE. Анклав генерирует подтвержденный локальный аттестат для целевого анклава, используя инструкцию ereport. Этот аттестат может быть криптографически проверен целевым анклавом с помощью ключа, полученного инструкцией egetkey.

В свою очередь, SGX основан на более ранней технологии от Intel EPID. Алгоритм Enhanced privacy ID был разработан в 2008 году и до сих пор используется как часть механизма аттестации в доверенных системах, таких как SGX.

Анклавы SGX находятся в виртуальном адресном пространстве, но их физическая память поддерживается защищенным кешем страниц анклава (Enclave Page Cache, EPC). Записи в EPC автоматически шифруются и при необходимости расшифровываются механизмом шифрования памяти. Информация из анклава недоступна для злоумышленников или вредоносных программ, так как находится в зашифрованном состоянии. Если во время работы анклава происходит сбой или прерывание, процессор инициирует асинхронный выход из анклава (AEX), надежно сохраняя и очищая все регистры процессора, где выполняется анклав, на момент прерывания в области сохранения его состояния (SSA) внутри EPC.

Из‑за ограниченного размера EPC зашифрованные страницы могут перемещаться в основную память и обратно без раскрытия их содержимого. Когда страница анклава перемещается из основной памяти обратно в EPC, ее расшифровывают и криптографически проверяют, чтобы убедиться, что ее содержимое не было подделано или изменено. Однако при этом данные в открытом виде попадают в кеш процессора. Выполнение анклавов может быть начато только из предварительно подготовленной точки входа с помощью инструкции eenter. Завершение выполнения — с использованием инструкции eexit. Специальная инструкция eresume восстанавливает выполнение анклава из фрейма SSA.

Системное ПО использует инструкцию EWBдля перемещения зашифрованных страниц EPC из кеша в оперативную память. Когда страница анклава перемещается из оперативной памяти в кеш, используется инструкция ELDU. Она расшифровывает и криптографически проверяет содержимое, чтобы гарантировать, что оно не было подделано.

Как ты уже знаешь, для обработки запросов к кешам процессора разных уровней служат буферы. Исследователи установили, что в процессорах Intel суперочередь используется как временный буфер для хранения запросов APIC. Изучение механизма работы APIC показало, что при инициализации буфера APIC перезаписывает нулями только архитектурно определенные части регистра и оставляет неактуальные значения в зарезервированной его части. Иными словами, при чтении неопределенного диапазона регистров APIC из буфера возвращаются устаревшие данные, помещенные туда другим процессом, при этом чтение можно выполнить из Ring 0, то есть из операционной системы.

Настало время вспомнить о том, что буфер APIC хранится в суперочереди, а сама суперочередь отвечает за кеширование информации. Таким образом, через эти регистры могут быть прочитаны любые данные, передаваемые между L2 и кешем последнего уровня. В том числе и попавшие в кеш данные из страниц анклава, хранящиеся там в открытом виде.

ЭКСПЛУАТАЦИЯ

Для эксплуатации уязвимости AEPIC Leak исследователи предложили две техники: Cache Line Freezing и Enclave Shaking. Обе техники нацелены на получение из суперочереди значений регистров, состояния загрузки памяти, а также кешированных страниц данных SGX-анклава. Уязвимость позволяет получить данные, используемые в процессе шифрования данных и удаленной аттестации, ключи AES-NI и RSA из библиотек Intel IPP и Intel SGX в течение нескольких секунд. Атака c использованием сочетания этих двух методов приводит к утечке данных из анклавов со скоростью 334,8 байт/с и коэффициентом успешности 92,2%.

Первый метод строится на получении строк состояния анклава (SSA) внутри EPC, когда работа анклава прерывается и зашифрованные страницы EPC перемещаются в основную память и обратно через буфер. Cache Line Freezing позволяет злоумышленнику точно выбирать получаемые из буфера номера строк кеш‑памяти и, таким образом, контролировать выборку строк. Без использования этого метода потребовались бы дополнительные инструменты, чтобы восстановить исходный порядок строк.

Метод Enclave Shaking использует возможности операционной системы безопасно менять местами страницы анклава. Попеременно меняя местами эти страницы, атакующий перемещает по иерархии кеша хранящиеся в них данные, что приводит к утечке значений даже без продолжения выполнения анклава. Иными словами, злоумышленник может сосредоточиться либо на области SSA для утечки данных, используемых в регистрах, либо на области секретных данных анклава в состоянии покоя. Повторяя атаку для каждой страницы анклава, можно полностью восстановить дамп памяти анклава и получить доступ к хранящимся в нем секретным данным.

Лучший результат достигается, если комбинировать обе атаки.

НАСКОЛЬКО ЭТО ОПАСНО?

Компания Intel прекратила поддерживать SGX в процессорах Core 11-го и 12-го поколений. Не вполне ясна ситуация с процессорами от других вендоров: AMD и Apple. Тем не менее уже выпущенные процессоры, работающие под управлением ПО без надлежащего обновления, по‑прежнему уязвимы. Также до сих пор уязвимость содержится в серверных процессорах Xeon третьего поколения, в них Intel пока не отключила SGX.

Для работы эксплуатирующей AEPIC Leak малвари требуются административные привилегии. Поэтому, если операционная система настроена правильно и злоумышленник не имеет доступа к учетной записи администратора, он не сможет воспользоваться уязвимостью. Однако, как было сказано выше, если подсунуть привилегированному юзеру эксплуатирующую эту уязвимость программу, то атака может быть успешна.

Что же касается гипервизоров, то процессоры Intel не раскрывают локальные регистры APIC для виртуальных машин, что устраняет угрозу гостевым системам. Тем не менее эксплуатация AEPIC Leak на «реальном железе» может привести к утечке данных из анклавов SGX, работающих на физическом ядре процессора. Это, в свою очередь, открывает злоумышленникам доступ к секретам DRM, ключам аттестации SGX, раскрывает AES-шифры и ставит под угрозу безопасность удаленных вычислений.

По большому счету уязвимость AEPIC Leak полностью разрушает гарантии безопасности, декларированные Intel для SGX, делая эту технологию практически бесполезной. Недаром Intel прекратила ее развитие и дальнейшую реализацию в новых процессорах.

КАК ОБЕЗОПАСИТЬ СВОИ ДАННЫЕ?

Независимые эксперты, а также сама корпорация Intel предлагают ряд решений, которые позволяют обезопасить данные от уязвимости AEPIC Leak.

- Отключить SGX. Без нее отсутствуют возможности эксплуатации уязвимости. Но это не вариант для систем, где SGX активно используется.

- В операционной системе включить режим x2APIC. Это позволит непосредственным образом отключить устаревший режим xAPIC. Главное отличие между xAPIC и x2APIC состоит в том, что последний не отображает на память регистры ввода/вывода, в первую очередь в целях повышения производительности. Поскольку x2APIC ничего не проецирует в память, украсть данные становится невозможно.

- Использовать обновленный SGX SDK.По заверениям представителей Intel, использование нового SDK снижает риск атак на брешь AEPIC Leak до минимума.

- Дождаться обновления микрокода. Intel может обновить микрокод в драйверах к своим устройствам или добавить его в качестве модулей операционной системы.

- Дождаться выхода новых процессоров, в которых аппаратная ошибка будет устранена.

Последние два варианта растянуты во времени на неопределенный срок. Тем не менее своевременное обновление ПО и аппаратной конфигурации позволяет повысить безопасность системы и избежать утечки критически важных данных.

Читайте ещё больше платных статей бесплатно: https://t.me/hacker_frei