АРХИТЕКТУРА ЭВМ

АнархистПРОЦЕССОР

ПРОЦЕССОР – ДЕШИФРУЕТ И ВЫПОЛНЯЕТ КОМАНДЫ ПРОГРАММЫ, ОРГАНИЗУЕТ ОБРАЩЕНИЕ К ПАМЯТИ, ИНИЦИИРУЕТ РАБОТУ ВНЕШНИХ УСТРОЙСТВ, ВОСПРИНИМАЕТ И ОБРАБАТЫВАЕТ ЗАПРОСЫ ПРЕРЫВАНИЯ.

БРП – блок регистровой памяти. Используется для хранения операндов, а также индексов или адресов для обращения к ОЗУ. Эти регистры имеют более высокое быстродействие, чем ОЗУ.

Блок Связи с ОЗУ – организует обмен инфой между проциком и ОЗУ, а также связь с переферией.

УУ – вырабатывает последовательность управляющих сигналов, инициирующих выполнение отдельных команд.

БУР – блок управляющих регистров. Предназначен для хранения управляющей инфы. Содержит регистры и счетчики, участвующие в управлении выч. Процессом. Регистр состояния проца, регистр запроса прерывания, счетчик команд.

Счетчик команд служит для определения адреса след. Исполняемой команды.

Схему делит можно на 2 части:

1) Управляющий блок (УУ, БУР)

2) Операционный блок ( БРП, АЛУ, Интерфейс связи с ОЗУ)

Организация памяти ЭВМ

Основные операции в памяти – это запись и чтение (операции обращения). Важными харками запоминающих устройств являются емкость и быстродействие.

Классификация запоминающих устройств:

1) По реализуемым в памяти операциям обращения

А) память с произвольным обращением (ОЗУ или RAM)

Б) память только для чтения (ПЗУ или ROM)

2) по способу организации доступа:

А) память с непосредственным или произвольным доступом (Время доступа к любой ячейке памяти не зависит от номера ячейки)

Б) память с прямым или циклическим доступом (возможность циклического времени доступа , CD, DVD, ПЗУ)

В) память с последовательным доступом (память на магнитных лентах)

Иерархическая структура памяти:

Блоки расположены по убыванию быстродействия и возрастанию емкости.

Алгоритмы

Кэш или кеш — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше осуществляется быстрее, чем выборка исходных данных из более медленной памяти или удаленного источника, однако её объём существенно ограничен по сравнению с хранилищем исходных данных.

Кэш с прямым отображением. Адрес памяти однозначно определяет строку

кэша, в которую будет помещен блок информации.

+ Простая схемная реализация, т.к. происходит одна операция сравнения тегов.

Недостаток – жесткое закрепление областей ОЗУ к строкам кэша по среднему полю адреса.

Кэш с полностью ассоциативным отображением позволяет преодолеть недостаток прямого, разрешая загрузку любого блока ОП в любую строку кэш-памяти. Два поля: поле тега и номер байта.

+ Отсутствие привязки областей ОЗУ к строкам Кэша.

- Сложная схема реализации из-за необходимости одновременного сравнения тега адреса с тегами всех строк кэша.

Множественно-ассоциативный тип или частично-ассоциативный тип отображения – это один из возможных компромиссов, сочетающий достоинства прямого и ассоциативного способов. Кэш-память (и тегов и данных) разбивается на некоторое количество модулей. Зависимость между модулем и блоками ОП такая же жесткая, как и при прямом отображении. А вот размещение блоков по строкам модуля произвольное и для поиска нужной строки в пределах модуля используется ассоциативный принцип. Этот способ отображения наиболее широко распространен в современных микропроцессорах.

АЛГОРИТМЫ ЗАМЕЩЕНИЯ СТРОК

1) В кэш памяти с прямым отображением ВСЕГДА замещается та строка, к которой только что было неудачное обращение и никакой другой выбор удаляемой строки здесь невозможен.

2) В полностью ассоциативной и частично ассоц. Необходим специальный алгоритм замещения.

Все алгоритмы замещения реализуются аппаратно.

4 алгоритма в порядке убывания их относительной эффективности:

1) LRU List Recently used наиболее давнее использование. Замешается строка к которой больше всего не было обращения. 2 способа аппаратной реализации:

1) При помощи счетчика

2) При помощи очереди, в очереди хранятся ссылки на строки. При обращении к строке ссылка перемещается в конец очереди. Замещается строка, ссылка на котрую оказывается первой в очереди.

2. FIFO алгоритм работает по принципу очереди, т.е. замещается строка дольше всего находившаяся в КЭШ памяти. При обращении к строке ссылка на нее никуда не перемещается.

3) LFU Lеast frequently used Суть его - замена наименее часто использованной строки. Замещается строка с наименьшим числом обращений. Реализуется путем связки каждой строки со счетчиком обращений.

4) Random случайный выброс строки замещения. Реализован может быть с помощью счетчика.

СПОСОБЫ ЗАПИСИ ИНФЫ В КЭШ ПАМЯТЬ

1) Метод сквозной записи – запись сначала ОЗУ (сквозь КЭШ), а затем и в кэш память в случае КЭШ-попадания. В случае Кэш промаха, либо происходит занесение в кэш (сквозная запись отображения), либо нет (сквозная запись без отображения)

+ ОЗУ всегда имеет свежую копию данных, простая схема реализации.

- На одну операцию изменения приходится две операции записи.

2) Метод обратной записи – запись происходит только в кэш память. Если в кэше находится строка, которой идет обращение (кэш попадание) в случае кэш промаха инфа записывается сразу в ОЗУ. При кэш попадании запись в ОЗУ происходит только при замещении строки кэша.

+ Запись осуществляется со скоростью кэш памяти при этом на несколько операции записи в кэш может приходиться всего одна запись в озу

- Сложная схемная реализация.

АДРЕСНАЯ ПАМЯТЬ

Способ организации памяти зависит от метода размещения и поиска инфы в запоминающем устройстве. По этому признаку различают адресную и стековую память.

Адресная память – размещение и поиск инфы основан на использовании адреса в качестве адреса используется порядковый номер ячейки запоминающих устройств

При обращении к запоминающему устройству – указывается номер ячейки памяти, в которой будет лежать инфа. Для приема адреса служит регистр RGA. Далее адрес идет дешифратор DC, который формирует активный сигнал на одном из своих выходов, номер которого определяется поступившим адресом. Таким образом DC указывает ячейку памяти, к которой происходит обращение.

При чтении инфы из запоминающего устройства УУ формирует управляющий сигнал чтения под действием, которого прочитанная из ЗМ (запоминающий массив) слово поступает в усилитель чтения. А оттуда в регистр инфы RGI.

При записи инфы записанное слово со входной ШД поступает в регистр инфы, а оттуда через усилитель записи под действием сигнала записи выбранную ячейку запоминающего массива. В качестве запоминающего элемента ЗМ используется конденсатор и запирающий транзистор.

+ Низкая стоимость , большая емкость. – Меньшее быстродействие.

КЭШ ПАМЯТЬ

Строится по технологии статической памяти.

+ Высокое быстродействие

- меньшая плотность упаковки на кристалле, высокая стоимость.

Стековая память является безадресной памятью, представляет собой совокупность ячеек (массив, в котором соседние ячейки связаны с друг другом разрядными цепями слов) Запись слов всегда происходит в верхнюю ячейку, при этом все ранее записанные слова сдвигаются вниз на одну ячейку.

Чтение также производится из верхней ячейки в порядке обратном порядку записи. В такой последовательности порядок чтения и записи соответствует правилу – LIFO. На практике стековую память можно организовать, используя адресную память.

Стеки со скользящей вершиной – сами данные никуда не перемещаются относительно данных происходит перемещение указателя вершины стека.

ФОРМАТЫ КОМАНД И РЕЖИМЫ АДРЕСАЦИИ ПРОЦЕССОРА

МП Intel 80486

1) Реальный режим (8086)

2) Защищенный режим(386+)

БС – блок сегментации, БУС – блок управления страницами, БПК – блок предвыборки команд, БДК – блок дешифрации команд.

Операционный блок вместе с ОУ предназначен для выполнения всех арифметических и логических операций. В ОУ содержится 8 32-разрядных РОН. БВК реализует 2-хступенчатый алгоритм конверизации и состоит из БПК и дешифратора команд.

БПК принимает команды из магистрали и создается очередь команд. БДК определяет тип и формат команды, номера используемых регистров. Диспетчер памяти состоит из БС и осуществляет 2-хступенчатое формирование физического адреса ячейки памяти.

Два режима работы процика:

1) Реальный (страничная организация памяти не используется, работает как МП 8086)

2) В защищенном режиме возможен многозадачный режим работы ( возможность страничной организации памяти) ОЗУ разбивается на сегменты. Сегменты могут разбиваться на страницы. Интерфейс магистрали предназначен для обмена инфой между МП, ОЗУ и переферией.

РЕГИСТРЫ ВХОДЯЩИЕ В СОСТАВ МП

Сегментные регистры 16-разрядные:

CS (Code segment), SS (Stack segment), Data segment: DS, ES, FS, GS. В реальном режиме содержимое сегментного регистра используется для хранения базового адреса сегмента. В Защищенном режиме используется как селектор дискриптора сегмента. Сегментация памяти и вычисление адресов в реальном режиме.

БА сегмента хранится в сегментном регистре. Сегмент состоит из смежных ячеек памяти. Является независимой и отдельно адресуемой единицей памяти объемом 64 кб. Каждому сегменту назначается начальный или базовый адрес. Это базовый адрес сегмента. В каждом сегментном регистре содержится 16 старших разрядов базового адреса. 4 младших разряда считаются нулевыми и автоматически приписываются к содержимому сегментного регистра. ФА является 20-разрядным для вычисления физического адреса БА суммируется с внутрисегментным смещением, которое определяет расстояние от начала сегмента до адресуемой ячейки. Внутрисегментное смещение – эффективный адрес ЕА.

ФОРМАТЫ КОМАНД МП ИНТЕЛ В РЕАЛЬНОМ РЕЖИМЕ

Размер команды в реальном режиме может составлять от 1 до 6 байт.

СИСТЕМЫ ВВОДА/ВЫВОДА

Технически система ввода/вывода в рамках ВМ реализуется комплексом модулей ввода/вывода (МВВ). Модуль ввода/вывода выполняет сопряжение ВУ с ЭВМ и различные коммуникационные операции между ними. Две основные функции МВВ:

- обеспечение интерфейса с ЦП и памятью («большой» интерфейс);

- обеспечение интерфейса с одним или несколькими периферийными устройствами («малый» интерфейс).

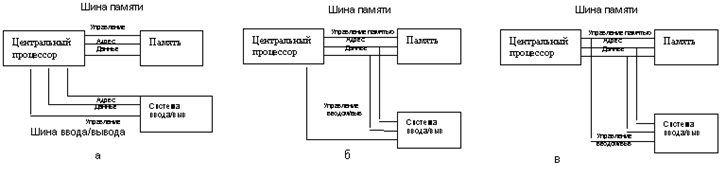

Анализируя архитектуру известных ВМ, можно выделить три основных способа подключения СВВ к ядру процессора.

В варианте с раздельными шинами памяти и ввода/вывода (см. рис. 1, а) обмен информацией между ЦП и памятью физически отделен от ввода/вывода, поскольку обеспечивается полностью независимыми шинами. Это дает возможность осуществлять обращение к памяти одновременно с выполнением ввода/вывода. Кроме того, данный архитектурный вариант ЭВМ позволяет специализировать каждую из шин, учесть формат пересылаемых данных, особенности синхронизации обмена и т.п. Недостатком решения можно считать большое количество точек подключения к ЦП.

Второй вариант — с совместно используемыми линиями данных и адреса (см. рис. 1, б). Память и СВВ имеют общие для них линии адреса и линии данных, разделяя их во времени. В то же время управление памятью и СВВ, а также синхронизация их взаимодействия с процессором осуществляются независимо по раздельным линиям управления. Это позволяет учесть особенности процедур обращения к памяти и к модулям ввода/вывода и добиться наибольшей эффективной доступа к ячейкам памяти и внешним устройствам.

Последний тип архитектуры ВМ предполагает подключение СВВ к системной шине на общих правах с процессором и памятью (см. рис. 1, в).

Преимущества: простота и низкая стоимость.

Недостатки: такое подключение не в состоянии обеспечить высокие интенсивность и скорость операций на шине.

Адресное пространство системы ввода/вывода

Адресное пространство ввода/вывода может быть совмещено с адресным пространством памяти или быть выделенным.

При совмещении адресного пространства для адресации модулей ввода/вывода отводится определенная область адресов (рис. 2). Обычно все операции с модулем ввода/вывода осуществляются с использованием входящих в него внутренних регистров: управления, состояния, данных. Фактически процедура ввода/вывода сводится к записи информации в одни регистры МВВ и считыванию ее из других регистров. Это позволяет рассматривать регистры МВВ как ячейки основной памяти и работать с ними с помощью обычных команд обращения к памяти, при этом в системе команд ВМ вообще могут отсутствовать специальные команды ввода и вывода. Так, модификацию регистров МВВ можно производить непосредственно с помощью арифметических и логических команд. Адреса регистрам МВВ назначаются в области адресного пространства памяти, отведенной под систему ввода/вывода.

Достоинства совмещенного адресного пространства:

- Расширение набора команд для обращения к внешним устройствам, что позволяет сократить длину программы и повысить быстродействие;

- Значительное увеличение количества подключаемых внешних устройств;

- возможность внепроцессорного обмена данными между внешними устройствами, если в системе команд есть команды пересылки между ячейками памяти;

- возможность обмена информацией не только с аккумулятором, но и с любым регистром центрального процессора.

Недостатки совмещенного адресного пространства:

- сокращение области адресного пространства памяти;

- усложнение декодирующих схем адресов в СВВ;

- трудности распознавания операций передачи информации при вводе/выв среди других операций.

Сложности в чтении и отладке программы, в которой простые команды вызывают выполнение сложных операций ввода/вывода;

Достоинства выделенного адресного пространства:

- адрес внешнего устройства в команде ввода/вывода может быть коротким. В большинстве СВВ количество внешних устройств намного меньше количества ячеек памяти. Короткий адрес ВУ подразумевает такие же короткие команды ввода/вывода и простые дешифраторы;

- программы становятся более наглядными, так как операции ввода/вывода выполняются с помощью специальных команд;

- разработка СВВ может проводиться отдельно от разработки памяти.

Недостатки выделенного адресного пространства:

- ввод/вывод производится только через аккумулятор центрального процессора. Для передачи информации от ВУ в РОН, если аккумулятор занят, требуется выполнение четырех команд (сохранение содержимого аккумулятора, ввод из ВУ, пересылка из аккумулятора в РОН, восстановление содержимого аккумулятора);

- перед обработкой содержимого В У это содержимое нужно переслать в ЦП.

Внешние устройства

Связь ВМ с внешним миром осуществляется с помощью самых разнообразных внешних устройств. Каждое ВУ подключается к МВВ посредством индивидуальной шины. Интерфейс, по которому организуется такое взаимодействие МВВ и ВУ и часто называют малым. Индивидуальная шина обеспечивает обмен данными и управляющими сигналами, а также информацией о состоянии участников обмена. Внешнее устройство, подключенное к МВВ, обычно называют периферийным устройством (ПУ). Все множество ПУ можно свести к трем категориям :

- для общения с пользователем (видеотерминалы и принтеры)

- для общения с ВМ; внешние запоминающие устройства (магнитные и оптические диски, магнитные ленты и т. п.), датчики и исполнительные механизмы

- для связи с удаленными устройствами.

Сигналы управления определяют функцию, которая должна быть выполнена внешним устройством. Логика управления — это схемы, координирующие работу ВУ в соответствии с направлением передачи данных.

Модули ввода/вывода

Функции модуля

Модуль ввода/вывода в составе вычислительной машины отвечает за управление одним или несколькими ВУ и за обмен данными между этими устройствами с одной стороны, и основной памятью или регистрами ЦП — с другой. Основные функции МВВ можно сформулировать следующим образом:

- локализация данных;

- управление и синхронизация;

- обмен информацией;

- буферизация данных;

- обнаружение ошибок.

Структура модуля ввода-вывода

Структура МВВ в значительной мере зависит от числа и сложности внешних устройств, которыми он управляет, однако в самом общем виде такой модуль можно представить в форме, показанной на рис. 3.

Связь модуля ввода/вывода с ядром ВМ осуществляется посредством системной или специализированной шины.

Данные, передаваемые в модуль и из него, буферизируются в регистре данных. Буферизация позволяет компенсировать различие в быстродействии ядра ВМ и внешних устройств.

Помимо регистра данных в составе МВВ имеются также регистр управления и регистр состояния (либо совмещенный регистр управления/состояния).

В регистре управления (РУ) фиксируются поступившие из ЦП команды управления модулем или подключенными к нему внешними устройствами. Отдельные разряды регистра могут представлять такие команды, как очистка регистров МВВ, сброс ВУ, начало чтения, начало записи и т. п.

Регистр состояния (PC) служит для хранения битов состояния MBВ и подключенных к нему ВУ. Содержимое определенного разряда регистра может характеризовать, например, готовность устройства ввода к приему очередной порции данных, занятость устройства вывода или нахождение ВУ в автономном режиме (offline).

Процедура ввода/вывода предполагает возможность работы с каждым регистром МВВ или внешним устройством по отдельности. Такая возможность обеспечивается системой адресации. Каждому модулю в адресном пространстве ввода/ вывода (совмещенном или раздельном) выделяется уникальный набор адресов, количество адресов в котором зависит от числа адресуемых элементов. Поступивший из ЦП адрес с помощью селектора адреса проверяется на принадлежность к диапазону, выделенному данному МВВ. В случае подтверждения дешифратор DC выполняет раскодирование адреса, разрешая работу с соответствующим регистром модуля или ВУ.

Узел управления вводом/выводом по сути играет роль местного устройства управления МВВ. На него возлагаются две задачи: обеспечение взаимодействия с ЦП и координация работы всех составляющих МВВ. Связь с ЦП реализуется посредством линий управления, по которым из ЦП в модуль поступают сигналы, служащие для синхронизации операций ввода и вывода. В обратном направлении передаются сигналы, информирующие о происходящих в модуле событиях, например сигналы прерывания. Часть линий управления может задействоваться модулем для арбитража. Вторая функция узла управления реализуется с помощью внутренних сигналов управления.

Со стороны «малого» интерфейса МВВ обеспечивает подключение внешних устройств и взаимодействие с ними. Каждое из внешних устройств «обслуживается» своим узлом «малого» интерфейса, который реализует принятый для данного ВУ стандартный протокол взаимодействия.

Методы управления вводом/выводом

В ЭВМ находят применение три способа организации ввода/вывода:

- программно управляемый ввод/вывод;

- ввод/вывод по прерываниям;

- прямой доступ к памяти.

При программно управляемом вводе/выводе все связанные с этим действия происходят по инициативе центрального процессора и под его полным контролем. ЦП выполняет программу, которая обеспечивает прямое управление процессом ввода/вывода, включая проверку состояния устройства, выдачу команд ввода или вывода. Выдав в МВВ команду, центральный процессор должен ожидать завершения ее выполнения, и, поскольку ЦП работает быстрее, чем МВВ, это приводит к потере времени.

Ввод/вывод по прерываниям во многом совпадает с программно управляемым методом. Отличие состоит в том, что после выдачи команды ввода/вывода ЦП не должен циклически опрашивать МВВ для выяснения состояния устройства. Вместо этого процессор может продолжать выполнение других команд до тех пор, пока получит запрос прерывания от МВВ, извещающий о завершении выполнения выданной команды В/ВЫВ. Как и при программно управляемом В/ВЫВ, ЦП отвечает за извлечение данных из памяти (при выводе) и запись данных в память (при вводе).

Повышение как скорости В/ВЫВ, так и эффективности использования ЦП обеспечивает третий способ В/ВЫВ – прямой доступ к памяти (ПДП). В этом режиме основная память и модуль ввода/вывода обмениваются информацией напрямую, минуя процессор.